Mikrochip-Design: Syntheseprozess kann Maßnahmen gegen Hardware-Angriffe aushebeln

Datum 06.11.2024

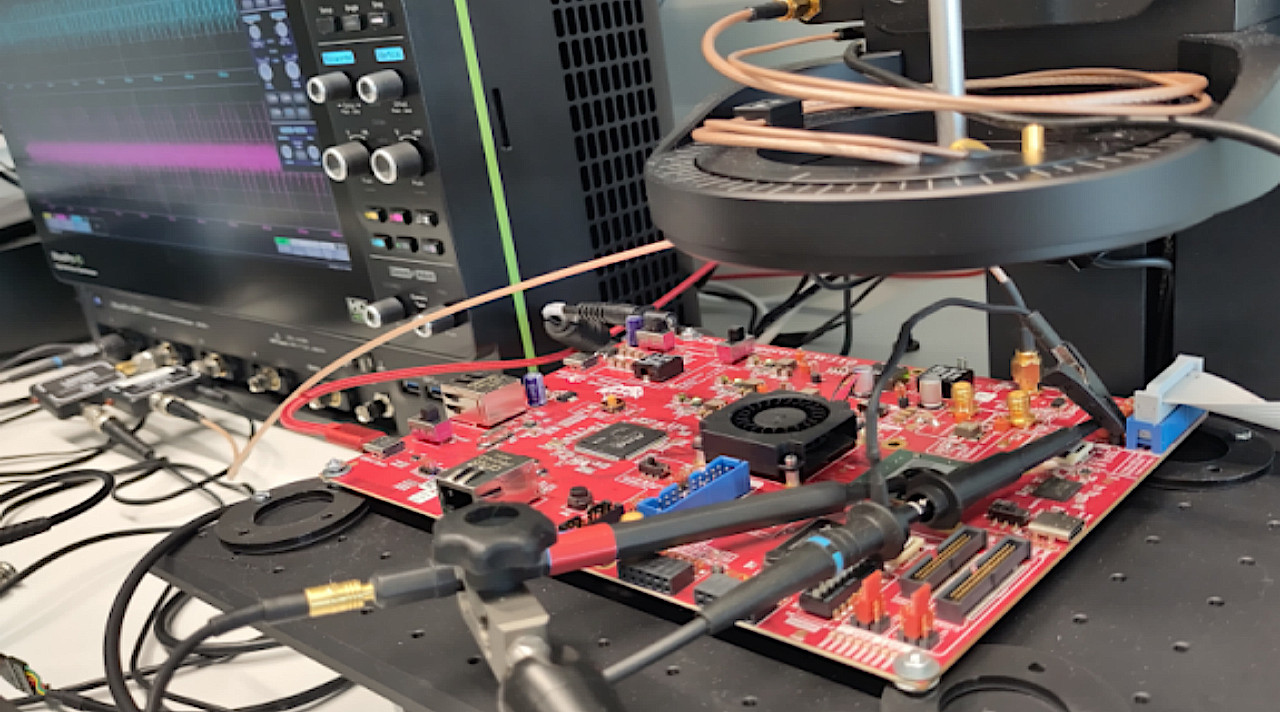

Das Fraunhofer-Institut AISEC hat im Auftrag des Bundesamts für Sicherheit in der Informationstechnik (BSI) die Studie „Security Evaluations of Hardware Design Synthesis“ erstellt. Sie beschreibt in mehreren Fallstudien, wie der Syntheseprozess im Mikrochip-Design vorhandene Maßnahmen gegen Hardware-Angriffe abschwächen oder sogar unwirksam machen kann. Exemplarisch werden Subsysteme des offenen Hardware-Designs Google Open Titan betrachtet. Mit der Publikation wollen BSI und Fraunhofer AISEC Produktentwickler und Hersteller für diese Risiken sensibilisieren.

Automatisierte Optimierungen gefährden Sicherheit

Der Entwurf von digitalen Chips beinhaltet mehrere Schritte. Er beginnt meist mit sehr abstrakten Blockdesigns, deren Funktionalität anschließend mittels einer Hardwarebeschreibungssprache wie etwa VHDL (Very High Speed Integrated Circuit Hardware Description Language) genau spezifiziert wird. Hieran schließt sich der Prozess der sogenannten „Synthese“ an, in dem der Code durch spezielle Softwaretools in eine technologiespezifische Netzliste umgewandelt wird. An dieser Stelle können die Designer auch Beschränkungen einfügen, wie etwa Flächenbeschränkungen oder die Vorgabe einer Zielfrequenz, mit welcher der Chip später betrieben werden soll. Um diese Vorgaben einhalten zu können, führen die Softwaretools diverse Optimierungen durch, die unter Umständen negative Auswirkungen auf bestimmte Funktionalitäten des Chips haben können.

Insbesondere in eingebetteten Systemen können bestimmte Sicherheitsmaßnahmen gegen sogenannte "Hardware-Angriffe" erforderlich sein. Diese Angriffe zielen nicht auf Schwachstellen in der Software, sondern auf inhärente Eigenschaften der Hardware. Solche Hardware-Angriffe umfassen unter anderem Seitenkanal- und Fehlerinjektions-Angriffe. Die implementierten Gegenmaßnahmen können sehr empfindlich auf Veränderungen des Designs durch den Syntheseprozess reagieren. Dies kann so weit gehen, dass manche ihre beabsichtigte Funktionalität nur noch teilweise oder auch gar nicht mehr erfüllen.

Die nun vorgelegte Studie dokumentiert diverse Fallstudien, in denen die Auswirkungen bestimmter Optimierungen auf in Hardware implementierte Maßnahmen gegen Seitenkanal- und Fehlerinjektions-Angriffe untersucht werden. Die Ergebnisse zeigen, dass die Einstellungen an den Synthesetools erhebliche Auswirkungen auf die Funktionalität der Sicherheitsmaßnahmen haben können oder diese sogar unabsichtlich weitestgehend deaktivieren können.

Optimierungseinstellungen sorgfältig wählen

In der Studie werden exemplarisch Subsysteme des Google Open Titan betrachtet. Dabei handelt es sich um ein offenes Hardware-Design, das frei synthetisiert und hergestellt werden darf. Dieses Open-Source Design enthält zahlreiche Sicherheitsmaßnahmen, die auch fortlaufend von der Community verifiziert werden. Dennoch können Sicherheitsprobleme auftreten, wenn die Optimierungseinstellungen der Synthesetools nicht sorgfältig gewählt werden.

Um diese Gefahr abzuwenden, sollten Designer die Einschränkungen ihrer Synthesetools genau kennen und Optimierungen entsprechend auswählen oder deaktivieren. Außerdem rät das BSI, die Forschung an Analysetools zu intensivieren. Ein erster Schritt dazu ist diese Studie. Weiterhin können auch unabhängige Sicherheitszertifizierungen, insbesondere des final synthetisierten Chips, die in der Studie identifizierten Probleme aufdecken.